## Coding Approaches to Fault Tolerance in Dynamic Systems

by

## Christoforos N. Hadjicostis

S.B., Massachusetts Institute of Technology (1993) M.Eng., Massachusetts Institute of Technology (1995)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

August 1999

Coplember 1993

Comparison of Technology 1999. All rights reserved.

Author...

Department of Electrical Engineering and Computer Science

August 12, 1999

Certified by

George C. Verghese

Professor of Electrical Engineering

Thesis Supervisor

Accepted by

Chairman, Departmental Committee on Graduate Students

Arthur C. Smith

#### Coding Approaches to Fault Tolerance in Dynamic Systems

bv

Christoforos N. Hadjicostis

Submitted to the Department of Electrical Engineering and Computer Science on August 12, 1999, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

A fault-tolerant system tolerates internal failures while preserving desirable overall behavior. Fault tolerance is necessary in life-critical or inaccessible applications, and also enables the design of reliable systems out of unreliable, less expensive components. This thesis discusses fault tolerance in dynamic systems, such as finite-state controllers or computer simulations, whose internal state influences their future behavior. Modular redundancy (system replication) and other traditional techniques for fault tolerance are expensive, and rely heavily — particularly in the case of dynamic systems operating over extended time horizons — on the assumption that the error-correcting mechanism (e.g., voting) is fault-free.

The thesis develops a systematic methodology for adding structured redundancy to a dynamic system and introducing associated fault tolerance. Our approach exposes a wide range of possibilities between no redundancy and full replication. Assuming that the error-correcting mechanism is fault-free, we parameterize the different possibilities in various settings, including algebraic machines, linear dynamic systems and Petri nets. By adopting specific error models and, in some cases, by making explicit connections with hardware implementations, we demonstrate how the redundant systems can be designed to allow detection/correction of a fixed number of failures. We do not explicitly address optimization criteria that could be used in choosing among different redundant implementations, but our examples illustrate how such criteria can be investigated in future work.

The last part of the thesis relaxes the traditional assumption that error-correction be fault-free. We use unreliable system replicas and unreliable voters to construct redundant dynamic systems that evolve in time with low probability of failure. Our approach generalizes modular redundancy by using distributed voting schemes. Combining these techniques with low-complexity error-correcting coding, we are able to efficiently protect identical unreliable linear finite-state machines that operate in parallel on distinct input sequences. The approach requires only a constant amount of redundant hardware per machine to achieve a probability of failure that remains below any pre-specified bound over any given finite time interval.

Thesis Supervisor: George C. Verghese Title: Professor of Electrical Engineering

### Acknowledgments

First and foremost, I would like to express my most sincere thanks to my thesis supervisor, Professor George Verghese, for his inspiring guidance and unlimited support throughout my graduate studies and research. Without his enthusiasm, encouragement and patience whenever I reached a point of difficulty, this thesis would not have reached its current form.

I am also extremely grateful to Professors Alan Oppenheim and Gregory Wornell for their direction, warm support, and hospitality over these years. Not only did their financial assistance make this thesis possible, but they also gave me the opportunity to work in an excellent academic environment that helped me mature as a researcher and as a person.

I am indebted to many members of the faculty at MIT for their involvement and contribution to my thesis work. My committee members, Professors Sanjoy Mitter and Alex Megretski, were a source for help and inspiration. Their challenging and thought-provoking questions have shaped many aspects of this thesis. Furthermore, the discussions that I had with Professors Bob Gallager, David Forney, Daniel Spielman, and Srinivas Devadas were also extremely encouraging and helpful in defining my research direction; I am very thankful to all of them.

I would also like to thank my many friends and fellow graduate students who made life at MIT both enjoyable and productive. Special thanks go to my "buddy" Carl Livadas who was there every time I needed to ask an opinion, or simply complain. Babis Papadopoulos and John Apostolopoulos were a great source of advice during the formative stages of this work (particularly during late hours!). Thanos Siapas gave me lots of feedback (and laughs) at the later stages of my thesis. Hisham Kassab, Sekhar Tatikonda, Costas Boussios, Chalee Asavathiratham, and Tony Ezzat were good friends and also extremely helpful with comments and suggestions.

I also want to acknowledge all members of the Digital Signal Processing Group for being great colleagues and friends. My time at the DSPG will remain an unforgettable experience. My special thanks to Stark Draper, Richard Barron, Nicholas Laneman, Matt Secor, Charles Sestok, and Jeff Ludwig. Giovanni Aliberti not only offered computer expertise, but was also a great friend; Darla Chupp, Vivian Mizuno, Maggie Beucler, Janice Zaganjori and Sally Bemus made life a lot simpler by meticulously taking care of administrative matters.

Finally, I am grateful to the Defense Advanced Research Projects Agency for support under the RASSP project, EPRI and the Department of Defense for support under the Complex Network Initiation, and the National Semiconductor Corporation and the Grass Instrument Company for their generous financial support. Peggy Carney's help with finding and administrating fellowship support is gratefully acknowledged; her assistance was most valuable for the completion of this work.

# Contents

| 1                                                    | Intr | oducti                                                              | ion and Background                                         | 15 |

|------------------------------------------------------|------|---------------------------------------------------------------------|------------------------------------------------------------|----|

|                                                      | 1.1  | Defini                                                              | tions and Motivation                                       | 15 |

|                                                      | 1.2  | Backg                                                               | round: Fault Tolerance in Computational Systems            | 17 |

|                                                      | 1.3  | Fault                                                               | Tolerance in Dynamic Systems                               | 22 |

|                                                      |      | 1.3.1                                                               | Redundant Implementation                                   | 25 |

|                                                      |      | 1.3.2                                                               | Error-Correction                                           | 28 |

|                                                      | 1.4  | Scope                                                               | and Major Contributions of the Thesis                      | 29 |

|                                                      | 1.5  | Outlin                                                              | ne of the Thesis                                           | 32 |

| 2                                                    | Red  | lundan                                                              | nt Implementations of Algebraic Machines                   | 33 |

|                                                      | 2.1  | Introd                                                              | luction                                                    | 33 |

|                                                      | 2.2  | 2.2 Background: Fault-Tolerant Computation in Groups and Semigroups |                                                            |    |

|                                                      |      |                                                                     |                                                            |    |

|                                                      |      | 2.2.1                                                               | Fault Tolerance in Abelian Group Computations              | 34 |

|                                                      |      | 2.2.2                                                               | Fault Tolerance in Semigroup Computations                  | 37 |

|                                                      | 2.3  | Redur                                                               | ndant Implementations of Algebraic Machines                | 41 |

|                                                      |      | 2.3.1                                                               | Redundant Implementations of Group Machines                | 42 |

|                                                      |      | 2.3.2                                                               | Redundant Implementations of Semigroup Machines            | 54 |

| 2.4 Redundant Implementations of Finite Semiautomata |      |                                                                     | ndant Implementations of Finite Semiautomata               | 59 |

|                                                      |      | 2.4.1                                                               | Characterization of Non-Separate Redundant Implementations | 62 |

|                                                      |      | 2.4.2                                                               | Characterization of Separate Redundant Implementations     | 64 |

|                                                      | 2.5  | Summ                                                                | nary                                                       | 67 |

| 3 | Red  | dundant Implementations of Linear Time-Invariant          |     |  |  |

|---|------|-----------------------------------------------------------|-----|--|--|

|   | Dyn  | namic Systems                                             | 69  |  |  |

|   | 3.1  | Introduction                                              | 69  |  |  |

|   | 3.2  | Linear Time-Invariant Dynamic Systems                     | 70  |  |  |

|   | 3.3  | Characterization of Redundant Implementations             | 71  |  |  |

|   | 3.4  | Hardware Implementation and Error Model                   | 74  |  |  |

|   | 3.5  | Examples of Fault-Tolerant Schemes                        | 77  |  |  |

|   | 3.6  | Summary                                                   | 89  |  |  |

| 4 | Red  | lundant Implementations of Linear Finite-State Machines   | 91  |  |  |

|   | 4.1  | Introduction                                              | 91  |  |  |

|   | 4.2  | Linear Finite-State Machines                              | 92  |  |  |

|   | 4.3  | Characterization of Redundant Implementations             | 95  |  |  |

|   | 4.4  | Examples of Fault-Tolerant Schemes                        | 97  |  |  |

|   | 4.5  | Summary                                                   | 106 |  |  |

| 5 | Fail | lure Monitoring in Discrete Event Systems Using Redundant |     |  |  |

|   | Pet  | ri Net Implementations                                    | 107 |  |  |

|   | 5.1  | Introduction                                              | 107 |  |  |

|   | 5.2  | Petri Net Models of Discrete Event Systems                | 108 |  |  |

|   | 5.3  | Error Model                                               | 112 |  |  |

|   | 5.4  | Monitoring Schemes Using Separate                         |     |  |  |

|   |      | Redundant Implementations                                 | 115 |  |  |

|   |      | 5.4.1 Separate Redundant Petri Net Implementations        | 115 |  |  |

|   |      | 5.4.2 Failure Detection and Identification                | 119 |  |  |

|   | 5.5  | Monitoring Schemes Using Non-Separate                     |     |  |  |

|   |      | Redundant Implementations                                 | 127 |  |  |

|   |      | 5.5.1 Non-Separate Redundant Petri Net Implementations    | 127 |  |  |

|   |      | 5.5.2 Failure Detection and Identification                | 133 |  |  |

|   | 5.6  | Applications in Control                                   | 137 |  |  |

|   |      | 5.6.1 Monitoring Active Transitions                       | 137 |  |  |

|   |      | 5.6.2 Detecting Illegal Transitions                       | 139 |  |  |

|                               | 5.7 | Summ    | ary                                                       | 142 |

|-------------------------------|-----|---------|-----------------------------------------------------------|-----|

| 6 Unreliable Error-Correction |     |         | Error-Correction                                          | 143 |

|                               | 6.1 | Introd  | uction                                                    | 143 |

|                               | 6.2 | Proble  | em Statement                                              | 144 |

|                               | 6.3 | Distril | outed Voting Scheme                                       | 145 |

|                               | 6.4 | Reliab  | le Linear Finite-State Machines Using Constant Redundancy | 150 |

|                               |     | 6.4.1   | Low-Density Parity Check Codes and Stable Memories        | 150 |

|                               |     | 6.4.2   | Reliable Linear Finite-State Machines                     | 154 |

|                               |     | 6.4.3   | Further Issues                                            | 160 |

|                               | 6.5 | Summ    | ary                                                       | 164 |

| 7                             | Con | clusio  | ns and Future Directions                                  | 167 |

| A                             | Con | dition  | s for Single-Error Detection and Correction               | 173 |

|                               | A.1 | Semig   | roup Computations                                         | 173 |

|                               | A.2 | Finite  | Semiautomata                                              | 175 |

| В                             | Pro | of of T | Cheorem 6.2                                               | 179 |

|                               | B.1 | "Stead  | ly-State" Under No Initial Propagation Failure            | 180 |

|                               | B.2 | Condi   | tional Probabilities Given No Initial Propagation Failure | 182 |

|                               | B.3 | Bound   | ls on the Probabilities of Failures                       | 184 |

|                               |     | B.3.1   | Bounding the Probability of Initial Propagation Failure   | 184 |

|                               |     | B.3.2   | Bounding the Probability of Overall Failure               | 107 |

# List of Figures

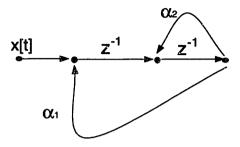

| 1-1 | Fault tolerance using an arithmetic coding scheme                        | 20  |

|-----|--------------------------------------------------------------------------|-----|

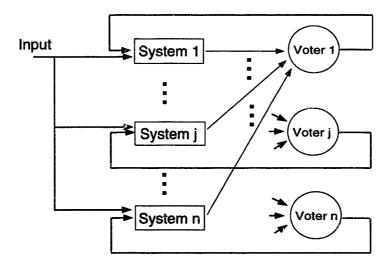

| 1-2 | Triple modular redundancy with correcting feedback                       | 24  |

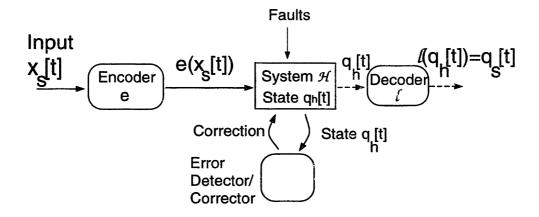

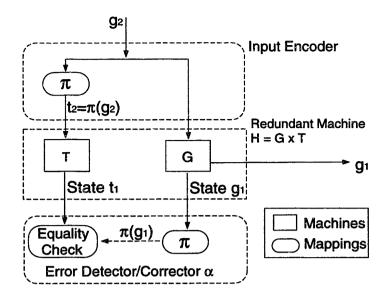

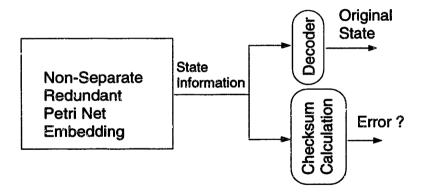

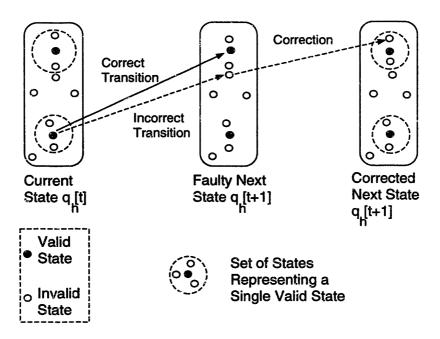

| 1-3 | Thesis approach for fault tolerance in a dynamic system                  | 26  |

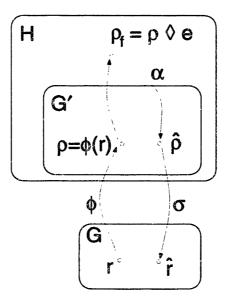

| 2-1 | Fault tolerance in a group computation using a homomorphic mapping       | 36  |

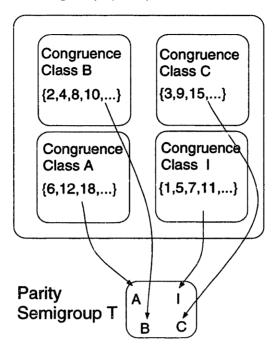

| 2-2 | Partitioning of semigroup $(N, \times)$ into congruence classes          | 40  |

| 2-3 | Error detection and correction in a redundant implementation of a group  |     |

|     | machine                                                                  | 43  |

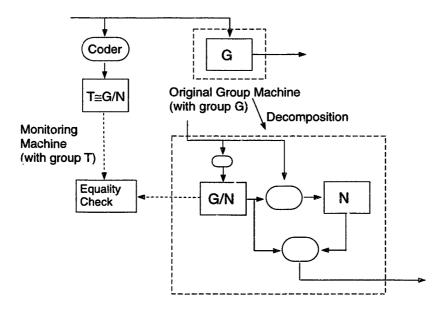

| 2-4 | Monitoring scheme for a group machine                                    | 45  |

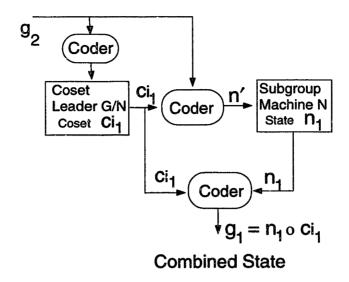

| 2-5 | Series-parallel decomposition of a group machine                         | 49  |

| 2-6 | Construction of a separate monitor based on group machine decomposition. | 50  |

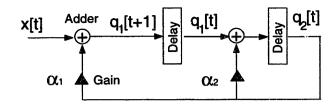

| 3-1 | Delay-adder-gain circuit and the corresponding signal flow graph         | 75  |

| 3-2 | Digital filter implementation using delays, adders and gains             | 80  |

| 3-3 | Redundant implementation based on a checksum condition                   | 81  |

| 3-4 | A second redundant implementation based on a checksum condition          | 83  |

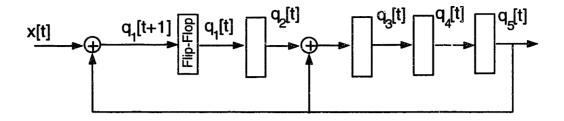

| 4-1 | Example of a linear feedback shift register                              | 92  |

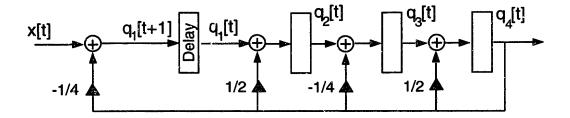

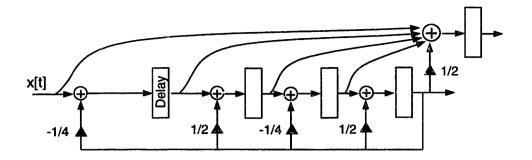

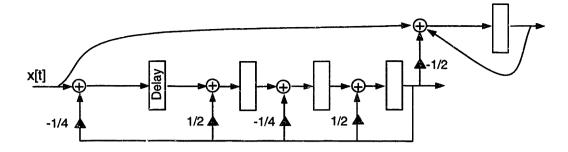

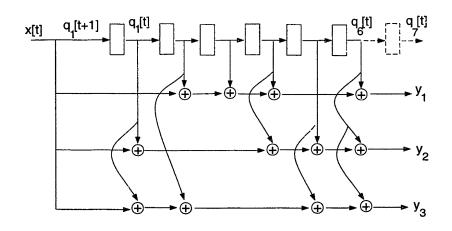

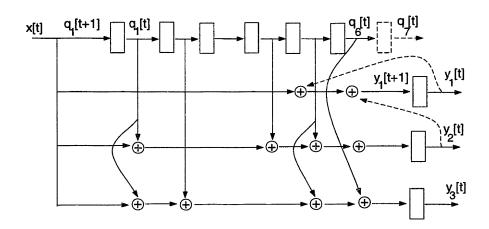

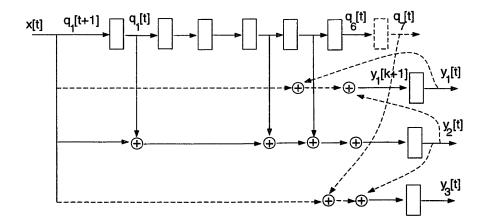

| 4-2 | Three different implementations of a convolutional encoder               | 100 |

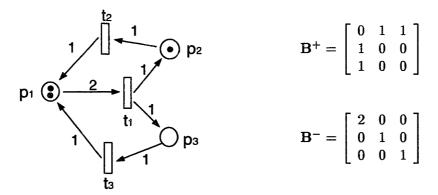

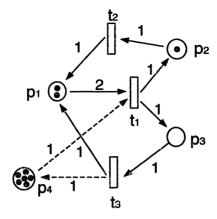

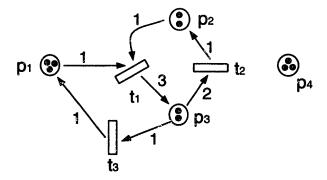

| 5-1 | Example of a Petri net with three places and three transitions           | 109 |

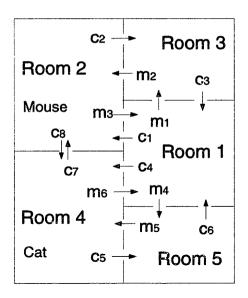

| 5-2 | Cat-and-mouse maze                                                       | 111 |

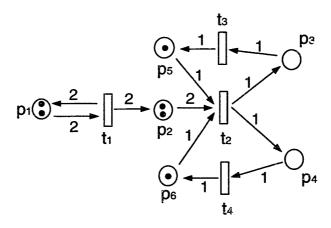

| 5-3 | Petri net model of a distributed processing system                       | 114 |

| 5-4 | Petri net model of a digital system.                                     | 115 |

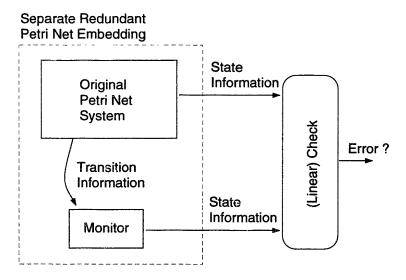

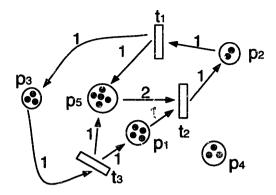

| 5-5 | Concurrent monitoring scheme for a Petri net                             | 116 |

| 5-6  | Example of a separate redundant Petri net implementation that identifies                    |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | single-transition failures in the Petri net of Figure 5-1                                   | 121 |

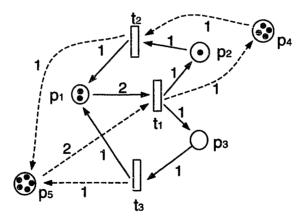

| 5-7  | Example of a separate redundant Petri net implementation that identifies                    |     |

|      | single-place failures in the Petri net of Figure 5-1                                        | 123 |

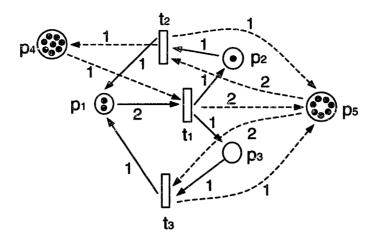

| 5-8  | Example of a separate redundant Petri net implementation that identifies                    |     |

|      | single-transition $or$ single-place failures in the Petri net of Figure 5-1                 | 125 |

| 5-9  | Concurrent monitoring using a non-separate Petri net implementation                         | 127 |

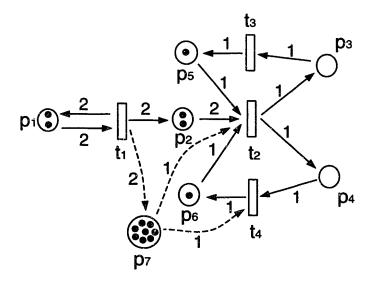

| 5-10 | Example of a non-separate redundant Petri net implementation that identifies                |     |

|      | single-transition failures in the Petri net of Figure 5-1                                   | 134 |

| 5-11 | Example of a non-separate redundant Petri net implementation that identifies                |     |

|      | single-place failures in the Petri net of Figure 5-1                                        | 136 |

| 5-12 | Example of a separate redundant Petri net implementation that enhances                      |     |

|      | control of the Petri net of Figure 5-3                                                      | 138 |

| 6-1  | Reliable state evolution using unreliable error-correction                                  | 146 |

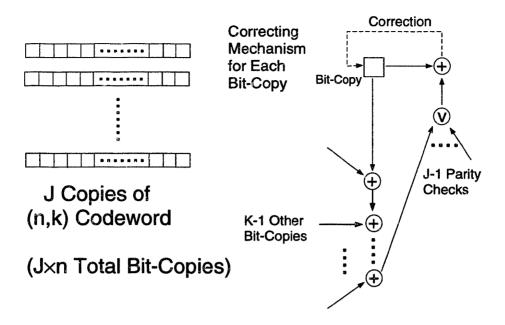

| 6-2  | Modular redundancy using a distributed voting scheme                                        | 147 |

| 6-3  | ${\bf Hardware\ implementation\ of\ the\ modified\ iterative\ decoding\ scheme\ for\ LDPC}$ |     |

|      | codes                                                                                       | 152 |

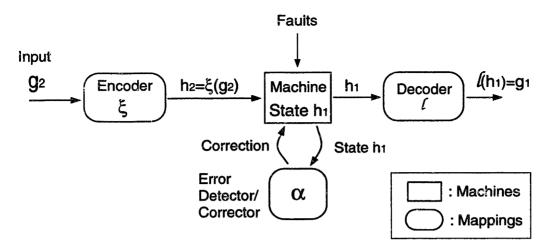

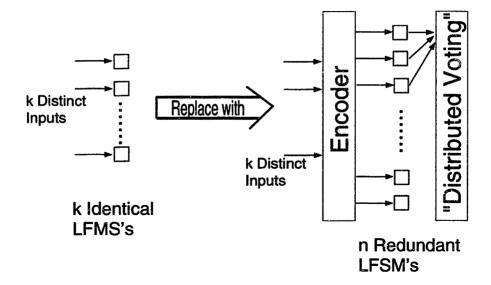

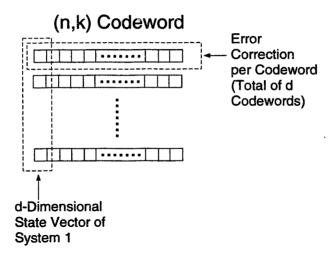

| 6-4  | Replacing $k$ LFSM's with $n$ redundant LFSM's                                              | 155 |

| 6-5  | Encoded implementation of $k$ LFSM's using $n$ redundant LFSM's                             | 157 |

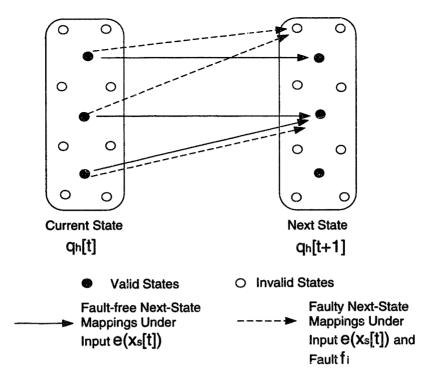

| A-1  | Conditions for single-error detection in a finite semiautomaton                             | 175 |

| A-2  | Con 'itions for single-error correction in a finite semiautomaton                           | 176 |

# List of Tables

6.1 Typical values for p,  $\beta$  and C given J, K,  $p_x$  and  $p_v$ . The bound on the probability of overall failure is shown for  $d=10,\,k=10^7$  and  $L=10^5,\,\ldots$  159

# Chapter 1

# Introduction and Background

#### 1.1 Definitions and Motivation

A fault-tolerant system tolerates internal failures and prevents them from unacceptably corrupting its overall behavior, output or final result. Fault tolerance is motivated primarily by applications that require high reliability (such as life-critical medical equipment, defense systems and aircraft controllers), or by systems that operate in remote locations where monitoring and repair may be difficult or even impossible (as in the case of space missions and remote sensors), [5, 85]. In addition, fault tolerance is desirable because it relaxes design/manufacturing specifications (leading for example to yield enhancement in integrated circuits, [59, 63, 80]), and also because it enables new technologies and the construction of reliable systems out of unreliable (possibly fast and inexpensive) components. As the complexity of computational and signal processing systems increases, their vulnerability to failures becomes higher, making fault tolerance necessary rather than simply desirable, [90]; the current trends towards higher clock speed and lower power consumption aggravate this problem even more.

Fault tolerance has been addressed in a variety of settings. The most systematic treatment has been for the case of reliable digital transmission through unreliable communication links and has resulted in error-correcting coding techniques that efficiently protect against channel noise, [95, 96, 38, 81, 11, 111]. Fault tolerance has also been used to protect com-

putational circuits against hardware failures. These failures<sup>1</sup> can be either *permanent* or *transient*: permanent failures could be due to manufacturing defects, irreversible physical damage, or stuck-at faults, whereas transient<sup>2</sup> failures could be due to noise, absorption of alpha particles or other radiation, electromagnetic interference, or environmental factors. Techniques for fault tolerance have also been applied at a higher level to protect special-purpose systems against a fixed number of "functional" failures, which could be hardware, software or other; these ideas were introduced within the context of algorithm-based fault tolerance techniques (see [50, 93]).

In this thesis we explore fault tolerance in *dynamic systems*:

**Definition 1.1** A dynamic (or state-space) system is a system that evolves in time according to some internal state. More specifically, the state of the system at time step t, denoted by q[t], together with the input at time step t, denoted by x[t], completely determine the system's next state according to a state evolution equation

$$q[t+1] = \delta(q[t], x[t]) .$$

The output y[t] of the system at time step t is based on the corresponding state and input, and is captured by the output equation

$$y[t] = \lambda(q[t], x[t])$$

.

Examples of dynamic systems include finite-state machines, digital filters, convolutional encoders, decoders, and algorithms or simulations running on a computer architecture over several time steps. This thesis will focus on failures that cause an unreliable dynamic system to take a transition to an incorrect state<sup>3</sup>. Depending on the underlying system and its actual implementation, these failures can be permanent or transient, and hardware or software. Due to the nature of dynamic systems, the effects of a state transition failure may last over several time steps; state corruption at a particular time step generally leads

<sup>&</sup>lt;sup>1</sup>For more details on hardware failures see [31, 109] and references therein.

<sup>&</sup>lt;sup>2</sup>A transient or temporal failure is a failure whose *cause* (but not necessarily the effect) appears only temporarily.

<sup>&</sup>lt;sup>3</sup>A study of this error model in the context of sequential VLSI circuits appears in [24].

to the corruption of the overall behavior and output at future time steps.

To understand the severity of the problem, consider the following situation: assume that an unreliable dynamic system (such as a finite-state machine that is constructed out of failure-prone gates) is subject to transient failures with a probability of making an incorrect transition (on any input at any given time step) that is fixed at  $p_s$ . If failures at different time steps are independent, then the probability that the system follows the correct state trajectory for L consecutive time steps is  $(1-p_s)^L$  and goes to zero exponentially with L. In general, the probability that we are in the correct state after L steps is also low<sup>4</sup>. This means that the output of the system at time step L will be erroneous with high probability (because it is calculated based on an erroneous state). Therefore, our first priority (and the topic of this thesis work) is to ensure that the system follows the correct state trajectory.

Before we discuss our approach for constructing fault-tolerant dynamic systems, we describe in more detail previous work on fault-tolerant *computational* circuits. The distinction between dynamic systems and computational circuits is that the former evolve in time according to their internal state (memory), whereas the latter have no internal state and no evolution with respect to time.

## 1.2 Background: Fault Tolerance in Computational Systems

A necessary condition for a computational system to be fault-tolerant is that it exhibit redundancy. "Structured redundancy" (that is, redundancy that has been intentionally introduced in some systematic way) allows a computational system to distinguish between valid and invalid results and, if possible, perform the necessary error-correction procedures. Structured redundancy can also be used to guarantee acceptably degraded performance despite failures. A well-designed fault-tolerant system makes efficient use of resources by adding redundancy in those parts of the system that are more liable to failures than others, and adding the redundancy in ways that are adapted to the operation of the system.

The traditional way of designing fault-tolerant computational systems that cope with

<sup>&</sup>lt;sup>4</sup>The probability that we are in the correct state after L steps depends on the structure of the particular finite-state machine, on the error model and on whether multiple failures may lead to a correct state. The argument can be made more precise if we choose a particular structure for our machine (consider for example a linear feedback shift register with failures that cause each bit in its state vector to flip with probability p).

hardware failures is to use N-modular hardware redundancy, [107]. By replicating the original system N times, we compute the desired function multiple times in parallel. The outputs of all replicas are compared and the final result is chosen based on what the majority of them agrees upon. Modular redundancy has been the primary methodology for fault-tolerant system design because it is universally applicable<sup>5</sup> and because it effectively decouples system design from fault tolerance design. Modular redundancy, however, is inherently expensive and inefficient due to system replication.

Research in communications has extensively explored alternative, more efficient ways of utilizing redundancy for achieving reliable digital transmission through an imperfect ("noisy") channel. In his seminal work [95, 96], Shannon showed that, contrary to the common perception of the time, one can send multiple bits encoded in a way that achieves arbitrarily low probability of error per bit with a *constant* amount of redundancy (per bit). This result generated a variety of subsequent work in information and coding theory, [38, 81, 11, 111].

In more complex systems that involve not only simple transmission of the data but also some simple processing on the data (e.g., boolean circuits or signal processing systems with no evolution over time) the application of such coding ideas becomes more challenging. In addition, as pointed out in [5, 83], there have traditionally been two different philosophies in terms of dealing with failures in computational systems:

• One school of thought designs systems in a way that allows detection and/or correction of a fixed number of failures. For example, numerous systems have been designed with the capability to detect/correct single failures assuming that the error detecting/correcting mechanisms are fault-free. (Triple modular redundancy, which protects against a single failure in any one subsystem but not in the voter, is perhaps the most common case.) These approaches are based on the premise that failures are rare (therefore, protecting against a fixed number of failures is good enough<sup>6</sup>) and that the error-correcting mechanism is much simpler than the actual system implementation. This approach has resulted in a lot of practical fault-tolerant systems, particularly for

<sup>&</sup>lt;sup>5</sup>A number of commercial and other systems have used modular redundancy techniques, [6, 45]; a comprehensive list can be found in [8].

<sup>&</sup>lt;sup>6</sup>For example, if failures are independent and happen with probability  $p \ll 1$ , then the probability of two simultaneous failures is of the order of  $p^2$ , which is very small compared to p.

special-purpose tasks, where the structure of the underlying algorithm and/or hard-ware configuration can be exploited in order to minimize the hardware overhead, or the complexity of the redundant system and the corresponding correcting mechanism. Such ideas have been explored in sorting networks [25, 102, 64], 2-D systolic arrays for parallel matrix multiplication [50, 56], other matrix operations [1, 23], convolution using the fast Fourier transform [10], and many others. Similar principles prevail in the design of self-checking systems, [88, 84]. In these systems we are interested in ensuring that any combination of a fixed number of failures (including failures in the error-detecting mechanism) will be detected.

• The second approach to fault tolerance focuses on building reliable systems out of unreliable components. As we add redundancy into a fault-tolerant system, the probability of failure per component remains constant. Thus, the larger the system, the more failures it has to tolerate, but the more flexibility we have in using the added redundancy/functionality to ensure that, with high probability, the redundant system will have the desirable behavior. Work in this direction started with von Neumann [107], and has been continued by many others [112, 106], mostly in the context of fault-tolerant boolean circuits (see [83] for a comprehensive list).

The idea of adding a minimal amount of redundancy in order to detect/correct a (prespecified) number of failures (i.e., the first of the two approaches described above) has been quite successful in cases where one can exploit structural features of a computation or an algorithm and introduce "analytical redundancy" in a way that offers more efficient fault coverage than modular redundancy (at the cost of narrower applicability and harder design). Work in this direction includes arithmetic codes, algorithm-based fault tolerance and algebraic techniques. We describe these ideas in more detail below:

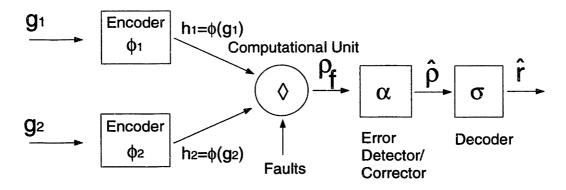

Arithmetic Codes: Arithmetic codes are error-correcting codes with properties that remain invariant under the arithmetic operations of interest, [87, 88]. They are typically used as shown in Figure 1-1 (which is drawn for the case of two operands, but more operands are handled in the same way). We first add "analytical redundancy" into the representation of the data by using suitable encodings, denoted by the mappings  $\phi_1$  and  $\phi_2$  in the figure. The desired original computation  $r = g_1 \circ g_2$  is then replaced

Figure 1-1: Fault tolerance using an arithmetic coding scheme.

by the modified computation  $\diamond$  on the encoded data. Under fault-free conditions, this modified operation produces  $\rho = \phi_1(g_1) \diamond \phi_2(g_2)$ , which results in r when decoded through the mapping  $\sigma$  (i.e.,  $r = \sigma(\rho)$ ). However, due to the possible presence of failures, the result of the redundant computation could be faulty,  $\rho_f$  instead of  $\rho$ . The redundancy in  $\rho_f$  is subsequently used to perform error detection and correction, denoted in the figure by the mapping  $\alpha$ . Note that the detector/corrector  $\alpha$  has no knowledge of the inputs and bases its decision solely on  $\rho_f$ . The output  $\hat{\rho}$  of the error detector and corrector is decoded through the use of the decoding mapping  $\sigma$ . Under fault-free conditions or with correctable failures,  $\hat{\rho}$  equals  $\rho$ , and the final result  $\hat{r}$  equals r. A common assumption in the model of Figure 1-1 is that the error detector/corrector is fault-free. This assumption is reasonable if the implementation of the decoder/corrector is simpler than the implementation of the computational unit (or if correcting occurs rarely). Another inherent assumption is that no failure takes place in the decoder unit; this assumption is in some sense inevitable: no matter how much redundancy we add, the output of a system will be faulty if the device that is supposed to provide the output fails (i.e., if there is a failure in the very last stage of the computational circuit/system). One way to avoid this problem is to assume that the output is provided to the user in an encoded form which can be correctly decoded by a fault-free final stage. In the modular redundancy case, for example, the output could be considered correct if the majority of the systems agree on the correct output (since a fault-free majority voter is then guaranteed to provide the correct output).

Algorithm-Based Fault Tolerance: More sophisticated coding techniques, known as Algorithm-Based Fault Tolerance (ABFT), were introduced by Abraham and coworkers [50, 56, 57, 74], starting in 1984. These schemes usually deal with arrays of real/complex data in concurrent multiprocessor systems. The classic example of ABFT is in the protection of  $M \times M$  matrix multiplication on a 2-D systolic array, [50]. A variety of computationally intensive algorithms, such as other matrix computations [50, 56], FFT computational networks [57], and digital convolution [10], have since been adapted to the requirements of ABFT.

As described in [56], there are three critical steps involved in ABFT schemes: (i) encoding the input data for the algorithm (just as for arithmetic coding), (ii) reformulating the original algorithm so that it can operate on the encoded data and produce decodable results, and (iii) distributing the computational tasks among the different subsystems of the failure-prone system so that any failures occurring within these subsystems can be detected and, hopefully, corrected. The above three steps are evident in the ABFT scheme for matrix multiplication that was presented in [50]. The encoding step involves adding an extra "checksum" row/column to the original  $M \times M$  matrices. The redundant operation involves multiplication of an  $(M+1) \times M$  matrix by an  $M \times (M+1)$  matrix. When using a 2-D systolic array to perform matrix multiplication, we manage to distribute both the computational tasks and the possible failures in a way that allows efficient failure detection, location and correction.

Algebraic Approaches: The most important challenge in both arithmetic coding and ABFT implementations is the recognition of structure in an algorithm that is amenable to the introduction of redundancy. A step towards providing a systematic approach for recognition and exploitation of such special structure was made for the case of computations that occur in a group or in a semigroup, [8, 9, 43, 44]. The key observation is that the desired analytical redundancy can be introduced by homomorphic embedding into a larger algebraic structure (group or semigroup). The approach extends

<sup>&</sup>lt;sup>7</sup>As mentioned earlier, this approach attempts to protect against a pre-specified maximum number of failures assuming fault-free error-correction. Some researchers have actually analyzed the performance of these schemes when the probability of failure in each component remains constant, [12, 103]. As expected, the scheme performs well if the probability of failure per component is very small.

to semirings, rings, fields, modules and vector spaces (i.e., algebraic structures that have the underlying characteristics of a semigroup or a group). A relatively extensive set of computational tasks can therefore be modeled using this framework. We give a brief overview of this approach in the beginning of Chapter 2.

The above mentioned approaches were mostly tailored for computational systems (systems without internal state) and assumed that error-correction is fault-free. As mentioned earlier, this assumption may be tolerable if the complexity of the correcting mechanism is considerably less than the complexity of the state evolution mechanism. Also, a fault-free output stage is in some sense inevitable: if all components may fail then, no matter how much redundancy we add, the output of a system will be faulty if the device that is supposed to provide the output fails (i.e., if there is a failure in the very last stage of the computation/circuit).

A significant aspect of any work on fault tolerance is the development of an appropriate error model. The error model describes the effect of failures on the output of a computational system, effectively allowing the mathematical study of fault tolerance. The error model does not have to mimic the actual fault mechanism; for example, we can model the error due to a failure in a multiplier as additive, or the error due to a failure in an adder as multiplicative<sup>8</sup>. Efficient error models need to be close to reality, yet general enough to allow algebraic or algorithmic manipulation. If a single hardware failure manifests itself as an unmanageable number of errors in the analytical representation, then the performance of our error detection/correction scheme will be unnecessarily complicated.

## 1.3 Fault Tolerance in Dynamic Systems

Traditionally, fault tolerance in dynamic systems has used modular redundancy. The technique is based on having replicas of the unreliable dynamic system, each initialized at the same state and supplied with the same inputs. Each system goes through the same sequence of states unless failures in the state transition mechanism cause deviations from this correct

<sup>&</sup>lt;sup>8</sup>The faulty result  $r_f$  of a real-number multiplier can always be modeled in an additive error fashion as  $r_f = r + e$  where r is the correct result and e is the additive error that has taken place. Similarly for the multiplicative representation of a failure in an adder (if  $r \neq 0$ ).

behavior. If we ensure that failures in the different system replicas are independent (e.g., by requiring that they are hardware- and/or software-independent), then the majority of the replicas at a certain time step will be in the correct state with high probability; an external voting mechanism can then decide what the correct state is using a majority voting rule.

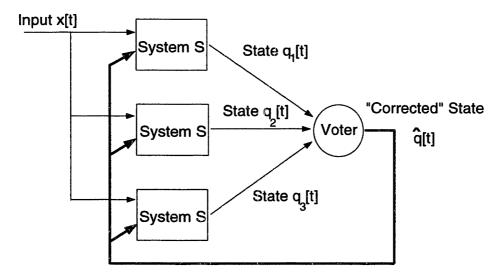

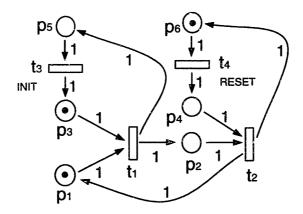

If we revisit the toy example of the unreliable dynamic system that makes a transition to an incorrect next state with probability  $p_s$  (independently at different time steps), we see that the use of majority voting at the end of L time steps may be highly unsuccessful: after a system replica operates (without error-correction) for L time steps, the probability that it has followed the correct sequence of states is  $(1-p_s)^L$ ; in fact, at time step L, a system replica may be in an incorrect state with a prohibitively high probability (for example, if an incorrect state is more likely to be reached than the correct one, then a voting mechanism will be unable to decide what the correct state/result is, regardless of how many times we replicate the system). One solution could be to correct the state of our systems at the end of each time step. This is shown in Figure 1-2: at the end of each time step, the voter decides what the correct state is, based on a majority voting rule; this "corrected" state is then fed back to all systems.

Another possibility could be to let the systems evolve for several time steps and then perform error-correction using a mechanism that is more complicated than a simple voter. For example, one could look at the *overall* state evolution (not just the final states) of all system replicas and then make an educated decision on what the correct state *sequence* is. A possible concern about this approach is that, by allowing the system to evolve incorrectly for several time steps, we may compromise system performance in the intervals between error-correction. We do not explore such alternatives in this thesis, mainly because we eventually allow failures in the error-correcting mechanism and and this is a rich issue even within the simpler setting.

The approach in Figure 1-2, more generally known as *concurrent error-correction*, has two major drawbacks:

$<sup>^9</sup>$ Given an initial state and a length-L input sequence, one can in principle calculate the probability of being in a certain state after L steps; the overall probability distribution will depend on the structure of the particular dynamic system, on the error model and on whether multiple failures may lead to the correct state.

<sup>&</sup>lt;sup>10</sup>We do not necessarily have to feed back the correct state at the end of each time step; if we feed it back after  $\tau$  steps, however, we need to ensure that  $(1 - p_s)^{\tau}$  does not become too small.

Figure 1-2: Triple modular redundancy with correcting feedback.

- System replication may be unnecessarily expensive. In fact, this was the original

motivation for arithmetic coding and ABFT schemes (namely the development of

fault-tolerant computational systems that make better use of redundancy by taking

into consideration the algorithmic structure of a given computational task).

- 2. The scheme relies heavily on the assumption that the voter is fault-free. If the voter also fails independently between time steps (e.g., with probability p<sub>v</sub> a voter outputs a state that is different from the state at which the majority of the systems agree), then we face a problem: after L time steps the probability that the modular redundancy scheme performs correctly is at best (1 p<sub>v</sub>)<sup>L</sup> (ignoring the probability that a failure in the voter may accidentally result in feeding back the correct state in cases where most systems are in an incorrect state). Similarly, the probability that the majority of the replicas is in the correct state after L time steps is also very low. Clearly, given unreliable voters there appears to be a limit on the number of time steps for which we can guarantee reliable evolution using a simple replication scheme. Moreover, in a dynamic system setting, failures in the voting mechanism become more significant as we increase the number of time steps for which the fault-tolerant system operates. Therefore, even if p<sub>v</sub> is significantly smaller than p<sub>s</sub> (e.g., because the system is more complex than the voter), the probability that the modular redundancy scheme performs correctly is bounded above by (1-p<sub>v</sub>)<sup>L</sup> and will eventually become unacceptably

small for large enough L.

In this thesis we deal with both of the above problems. We initially aim to protect against a pre-specified number of failures using a fault-free correcting mechanism. To achieve this while avoiding replication and while using the least amount of redundancy, we introduce the concept of a redundant implementation, that is, a version of the dynamic system which is redundant and follows a restricted state evolution. Redundant implementations range from no redundancy to full replication and give us a way of characterizing and parameterizing constructions that are appropriate for fault tolerance. The thesis demonstrates and exploits certain flexibilities that exist when constructing redundant implementations. We make no systematic attempt to choose from among these different redundant implementations ones that are optimal according to a particular criterion; our examples, however, illustrate how such questions may be posed in future work.

We also address the case when failures in each component happen with constant probability, independently between different components and independently between time steps. This problem is much harder, as we can no longer guarantee that the fault-tolerant system will be in the right state at the end of each time step. We introduce techniques that deal with transient failures in the error-correcting mechanism by developing and analyzing the performance of a distributed voting scheme. Our approach uses redundancy in a way that ensures that, with high probability, the fault-tolerant system will be within a set of states that represent (and can be decoded to) the actual state; the goal then becomes to make efficient use of redundancy while achieving any given probability of failure. For example, by increasing redundancy we can increase the probability that a fault-tolerant system follows the correct state trajectory for a certain time interval. Our analysis is very general and provides a better understanding of the tradeoffs that are involved when designing fault-tolerant systems out of unreliable components. These include constraints on the probabilities of failure in the system/corrector, the length of operation and the required amount of redundancy.

#### 1.3.1 Redundant Implementation

In order to avoid replication when constructing fault-tolerant dynamic systems, we replace the original system with a larger, redundant system that preserves the state, evolution and

Figure 1-3: Thesis approach for fault tolerance in a dynamic system.

properties of the original system — perhaps in some encoded form. We impose restrictions on the set of states that are allowed in the larger dynamic system, so that an external mechanism can perform error detection and correction by identifying and analyzing violations of these restrictions. The larger dynamic system is called a redundant implementation and is part of the overall fault-tolerant structure shown in Figure 1-3: the input to the redundant implementation at time step t, denoted by  $e(x_s[t])$ , is an encoded version of the input  $x_s[t]$  to the original system; furthermore, at any given time step t, the state  $q_s[t]$  of the original dynamic system can be recovered from the corresponding state  $q_h[t]$  of the redundant system through a decoding mapping  $\ell$  (i.e.,  $q_s[t] = \ell(q_h[t])$ ). Note that we require the error detection/correction procedure to be input-independent, so that we ensure the next-state function is not evaluated in the error-correcting circuit.

The following definition formalizes the notion of a redundant implementation for a dynamic system:

**Definition 1.2** Let S be a dynamic system with state set  $Q_S$ , input set  $X_S$ , initial state  $q_s[0]$  and state evolution

$$q_s[t+1] = \delta_{\mathcal{S}}(q_s[t], x_s[t]) ,$$

where  $q_s[\cdot] \in Q_S$ ,  $x_s[\cdot] \in X_S$  and  $\delta_S$  is the next-state function. A dynamic system  $\mathcal H$  with

state set  $Q_{\mathcal{H}}$ , input set  $X_{\mathcal{H}}$ , initial state  $q_h[0]$  and state evolution equation

$$q_h[t+1] = \delta_{\mathcal{H}}(q_h[t], e(x_s[t]))$$

(where  $e: X_{\mathcal{S}} \longmapsto X_{\mathcal{H}}$  is an injective input encoding mapping) is a redundant implementation for  $\mathcal{S}$  if it concurrently simulates  $\mathcal{S}$  in the following sense: there exists one-to-one state decoding mapping  $\ell: Q'_{\mathcal{H}} \longmapsto Q_{\mathcal{S}}$  such that

$$\ell(\delta_{\mathcal{H}}(\ell^{-1}(q_s[t]), e(x_s[t]))) = \delta_{\mathcal{S}}(q_s[t], x_s[t])$$

for all  $q_s[\cdot] \in Q_S$ ,  $x_s[\cdot] \in X_S$ . The set  $Q'_{\mathcal{H}} = \ell^{-1}(Q_S) \subset Q_{\mathcal{H}}$  is called the subset of valid states in  $\mathcal{H}$ .

If we initialize the redundant implementation  $\mathcal{H}$  to state  $q_h[0] = \ell^{-1}(q_s[0])$  and encode the input  $x_s[\tau]$  using the encoding mapping e, the state of  $\mathcal{S}$  at all discrete-time steps  $\tau \geq 0$  can be recovered from the state of  $\mathcal{H}$  through the decoding mapping  $\ell$  (under fault-free conditions at least); this can be proved easily by induction. Knowledge of the subset of valid states allows an external error detecting/correcting mechanism to handle failures. Any failures that cause transitions to *invalid* states (i.e., states outside the subset  $Q'_{\mathcal{H}} = \{q'_h[\cdot] = \ell^{-1}(q_s[\cdot]) \mid \forall q_s[\cdot] \in Q_{\mathcal{S}}\}$ ) will be detected and perhaps corrected.

During each time step, the redundant implementation  $\mathcal{H}$  evolves to a (possibly corrupted) next state. We then perform error detection/correction by checking whether the resulting state is in the subset of valid states  $Q'_{\mathcal{H}}$  and by making appropriate corrections when necessary. When we apply this general approach to specific dynamic systems, we manage to parameterize different redundant implementations, develop appropriate error models, make connections with hardware and systematically devise schemes capable of detecting/correcting a fixed number of failures.

Note that our definition of a redundant implementation does not specify next-state transitions when the redundant system is in a state outside the set of valid states<sup>11</sup>. Due to this flexibility, there are multiple different redundant implementations for a given error detecting/correcting scheme. In many cases we will be able to systematically characterize

<sup>&</sup>lt;sup>11</sup>This issue becomes very important when the error detector/corrector is *not* fault-free.

and exploit this flexibility to our advantage (e.g., to minimize hardware or to perform error detection/correction periodically).

#### 1.3.2 Error-Correction

In Chapter 6 we describe how to handle transient failures<sup>12</sup> in both the redundant implementation and the error-correcting mechanism. We assume that components in our systems can suffer transient failures (more specifically, we assume that they can fail independently between components and between time steps) and describe implementations that operate with an arbitrarily small probability of failure for a specified (finite) number of steps. In particular, given an unreliable dynamic system (e.g., one that takes an incorrect state transition with probability  $p_s$  at any given time step) and unreliable voters (that fail with probability  $p_{\nu}$ ), we describe ways to guarantee that the state evolution of a redundant fault-tolerant implementation will be correct with high probability for any specified (finite) number of steps. Our scheme is a variation of modular redundancy and is based on using a distributed set of voters. We show that, under this very general approach, there is a logarithmic tradeoff between the number of time steps and the amount of redundancy. In other words, if we want to maintain a given probability of failure while doubling the number of time steps for which our system operates, we need to increase the amount of redundancy by a constant amount. For the case of linear finite-state machines, we show that there are efficient ways of protecting many identical machines that operate in parallel on distinct input sequences. In this special setting, our approach can achieve a low probability of failure for any finite time interval using only a constant amount of redundancy per machine.

Our techniques relate well to existing techniques that have been used in the context of "reliable computational circuits" or "stable memories". As in these cases, our approach can provide fault tolerance to a dynamic system (that is, low probability of failure over any pre-specified finite time interval) at the expense of system replication. More specifically, given a certain time interval, we can achieve a low probability of failure by increasing the

<sup>&</sup>lt;sup>12</sup>Permanent failures can be handled more efficiently using reconfiguration techniques rather than concurrent error detection and correction. In some sense, permanent failures are easier to deal with than transient failures. For example, if we are testing for permanent failures in an integrated circuit, it may be reasonable to assume that our testing mechanism (error-detecting mechanism) has been verified to be fault-free. Since such verification only needs to take place once, we can devote large amounts of resources and time in order to ensure the absence of permanent failures in this testing/correcting mechanism.

amount of redundancy; alternatively, for a given probability of failure, we can increase operation time (i.e., the length of time for which the fault-tolerant system needs to operate reliably for) by increasing the amount of redundancy. Our method ensures that, with high probability, our fault-tolerant system will go through a sequence of states that *correctly represent* the fault-free state sequence. More specifically, at each time step, the state of the redundant system is within a set of states that can be decoded to the state in which the fault-free system would be in. Note that this is the best we can do since all components at our disposal can fail.

## 1.4 Scope and Major Contributions of the Thesis

Fault tolerance in dynamic systems has traditionally been addressed using techniques developed for fault tolerance in computational circuits. This thesis generalizes these techniques, studies the implications that the dynamic nature of systems has on fault tolerance and develops a framework that encompasses most previous schemes for concurrent error detection and correction in dynamic systems.

Adopting the traditional assumption that the error detecting/correcting mechanism is fault-free, we describe fault-tolerant schemes that protect against a specified, constant number of failures. Our approach is systematic and our goal (in each of the cases we study) is two-fold: (i) develop appropriate error models and techniques that satisfy the error detecting/correcting requirements, and (ii) parameterize redundant implementations for use in conjunction with a given error detecting/correcting mechanism. We study a variety of different dynamic systems, specifically those listed below, and in some cases we are able to make explicit connections with redundant hardware implementations, hardware failure modes, and error detecting/correcting techniques. We do not specifically address the issue of choosing an optimal redundant implementation (e.g., one that minimizes the hardware or cost involved), but we point out related questions in our examples.

Algebraic Machines: We develop appropriate (algebraic) encoding and decoding mappings for group/semigroup machines and demonstrate that each encoding/decoding pair has a number of possible redundant implementations, which may offer varying fault coverage. Our approach in this setting is purely algebraic and hardwareindependent. We do not make connections with actual hardware implementations and hardware failure modes, but use algebraic techniques to illustrate how different (algebraic) machine decompositions may capture different sets of errors/failures. In particular, we show that certain decompositions are undesirable because the failures of interest are always undetectable. We also extend these results to redundant implementations of finite semiautomata. The virtue of our approach is that it focuses on the desired functionality of a redundant implementation and not on the specifics of a particular hardware construction; this allows the development of novel fault-tolerant hardware constructions.

Linear Dynamic Systems: We study redundant implementations for linear time-invariant dynamic systems and linear finite-state machines, obtaining in each case a characterization of all redundant implementations with states that are linearly constrained (encoded according to a linear code). We show that within this class of redundant implementations each pair of encoding and decoding mappings permits a variety of state evolution mechanisms. Thus, there is some fiexibility in terms of choosing the redundant implementation which was not considered in previous work. A variant of our core result has been known in the control community (for continuous-time linear dynamic systems) but was not developed in the context of fault tolerance. Our approach results in a systematic way of constructing redundant implementations and allows us to make explicit connections with hardware constructions and hardware failure modes. In addition, using this flexibility we demonstrate examples of implementations that require less hardware than traditional ones, and new schemes for fault tolerance (including parity check schemes with memory).

Petri Nets: Following a similar approach, we systematically develop embeddings of Petri net models of discrete event systems (DES). The idea is based on enforcing constraints on the state (marking) of a given Petri net in way that retains its properties and overall functionality while allowing easy detection and identification of failures that may occur in the underlying DES. This leads to monitoring schemes for DES of interest, such as network protocols or manufacturing systems. The approach is general and can handle a variety of error models. We focus primarily on separate embeddings in which

the functionality of the original Petri net is retained in its exact form. Using these embeddings we construct monitors that operate concurrently with the original system and allow us to detect and identify different types of failures by performing consistency checks between the state of the original Petri net and that of the monitor. The methods that we propose are attractive because the resulting monitors are robust to failures, they may not require explicit acknowledgments from each activity and their construction is systematic and easily adaptable to restrictions in the available information. We also discuss briefly how to construct non-separate Petri net embeddings. There are a number of interesting directions that emanate from this work, particularly in terms of optimizing our embeddings (e.g., to minimize communication cost or other quantities of interest). We do not explicitly address such optimization questions but rather focus on establishing this new approach, highlighting its potential advantages, and describing the different parameters of the problem.

Unlike the situation in static (computational) circuits, fault tolerance in dynamic systems requires considerations about error propagation, and forces us to consider the possibility of failures in the error detecting/correcting mechanism. The problem is that a failure causing a transition to an incorrect next state at a particular time step will not only affect the output at a particular time step (which may be an unavoidable possibility, given that we use failure-prone elements), but will also affect the state (and therefore the output) of the system at later times. In addition, the problem of error propagation intensifies as we increase the number of time steps for which the dynamic system operates. On the contrary, failures in the implementation of static circuits only affect the output at a particular time step but have no aftereffects on the future performance of the systems (they do not intensify as we increase the number of time steps for which the systems operate).

The thesis addresses the problem of failures in the error detecting/correcting mechanism and shows that our two-stage approach to fault tolerance can be used successfully (and, in some cases that we illustrate, efficiently) to construct reliable systems out of unreliable components. First, we develop a distributed voting scheme and show how it can be used to construct redundant systems that evolve reliably for any given finite number of time steps. Our approach is novel, but related techniques can be found in computational circuits and

stable memories. By combining this distributed voting scheme with low-complexity error-correcting codes, we construct interconnections of identical linear finite-state machines that operate in parallel on distinct inputs and use a *constant* amount of hardware per machine in order to achieve a desired low probability of failure for any finite number of time steps. We also make comparisons and connections with related work, and point out interesting future directions and possible improvements to our construction.

#### 1.5 Outline of the Thesis

This thesis is organized as follows:

Chapters 2 through 5 systematically explore the concurrent error detection/correction approach of Figure 1-3 for different dynamic systems under the assumption that the error-correcting mechanism is fault-free. In Chapter 2 we focus on algebraic machines (group and semigroup machines, and finite semiautomata); in Chapters 3 and 4 we study redundant implementations for linear time-invariant dynamic systems and linear finite-state machines; in Chapter 5 we use similar ideas to construct Petri net embeddings and obtain robust monitoring schemes for discrete event systems.

In Chapter 6 we develop ways to handle failures in the error-correcting mechanism, both for the general case and also for the special case of linear finite-state machines.

We conclude in Chapter 7 with a summary of our results and future research directions.

# Chapter 2

# Redundant Implementations of Algebraic Machines

### 2.1 Introduction

In this chapter we develop a general, hardware-independent characterization of fault-tolerant schemes for group/semigroup machines and for finite semiautomata. More specifically, we use homomorphic embeddings to construct redundant implementations for algebraic machines, describe the corresponding error detection/correction techniques, and demonstrate that for a particular encoding/decoding scheme there exist many possible redundant implementations, each offering potentially different fault coverage.

Throughout our development, we assume that the error detecting/correcting mechanism is fault-free<sup>1</sup> and focus on algebraically characterizing redundant implementations. We assume a hardware-independent error model in which failures cause incorrect state transitions in the redundant machine. In later chapters of the thesis the fruits of our abstract approach become clearer, as we make explicit connections to hardware implementations and hardware failures. For example, in Chapters 3 and 4 we outline such extensions for linear time-invariant dynamic systems (implemented using adder, gain and memory elements)

<sup>&</sup>lt;sup>1</sup>As mentioned in the Introduction, the assumption that the error detecting/correcting mechanism is fault-free appears in most concurrent error detection and correction schemes. It is a reasonable assumption in many cases, particularly if the error checking mechanism is much simpler than the state evolution mechanism. In Chapter 6 we extend our approach to handle failures in the error detecting/correcting mechanism.

and linear finite-state machines (implemented using XOR gates and flip-flops).

This chapter is organized as follows. In Section 2.2 we provide background on the use of group/semigroup homomorphisms in constructing fault-tolerant computational systems, [43, 44, 8, 9]. Then, in Section 2.3, we develop redundant implementations for group and semigroup machines (in Sections 2.3.1 and 2.3.2 respectively). Our approach results in an algebraic characterization of the different redundant implementations under a given encoding/decoding scheme and also leads to discussions about the role of machine decomposition. In Section 2.4 we make connections with redundant implementations for finite semiautomata. Finally, in Section 2.5 we summarize the theoretical approach of this chapter and the key insights that it has provided.

# 2.2 Background: Fault-Tolerant Computation in Groups and Semigroups

Before we discuss fault tolerance in algebraic machines, we present some previous results on fault-tolerant computation in systems with algebraic structure.

### 2.2.1 Fault Tolerance in Abelian Group Computations

A group  $(G, \circ)$  is a set of elements G together with a binary operation  $\circ$  such that the following are satisfied:

- For all  $g_1, g_2, g_3 \in G$ ,  $g_1 \circ g_2 \in G$  (closure) and  $g_1 \circ (g_2 \circ g_3) = (g_1 \circ g_2) \circ g_3$  (associativity).

- There is an element  $1_o$ , called the *identity element* such that for all  $g \in G$ ,  $g \circ 1_o = 1_o \circ g = g$ .

- For every  $g \in G$ , there is an inverse element  $g^{-1} \in G$  such that  $g^{-1} \circ g = g \circ g^{-1} = 1_{\circ}$ .

An abelian group also satisfies commutativity:

• For all  $g_1, g_2 \in G$ ,  $g_1 \circ g_2 = g_2 \circ g_1$ .

A computation that takes place in an abelian group is protected in [8] by a coding scheme like the one shown in Figure 1-1. Redundancy is added to the operands by the encoding mappings  $\phi_1$  and  $\phi_2$ , which map operands in the abelian group  $(G, \circ)$  (e.g.,  $g_1$  and  $g_2$  in the figure) to elements in a larger abelian group  $(H, \circ)$  (these elements are denoted by  $h_1$  and  $h_2$  in the figure). The original group operation  $\circ$  in G is replaced by the redundant group operation  $\circ$  in H. Ideally, under no failures, the result  $r = g_1 \circ g_2$  can be obtained via the decoding mapping  $\sigma$  from the result  $\rho = h_1 \circ h_2$  in the redundant group (i.e.,  $r = \sigma(\rho)$ ). The subset of valid results in H is given by the set  $G' = \{\phi_1(g_1) \circ \phi_2(g_2) \mid g_1, g_2 \in G\}$ . The objective is to utilize the redundancy that exists in H to provide fault tolerance for the computation in G. By imposing the requirement that under fault-free conditions the decoding mapping  $\sigma: G' \longmapsto G$  be one-to-one, it can be shown that the encoding mappings  $\phi_1$  and  $\phi_2$  need to be the same mapping, which we denote by  $\phi$ , and that  $\sigma^{-1} = \phi$ . Moreover,  $\phi$  is shown to be a group homomorphism: for all  $g_1, g_2 \in G$ , we have  $\phi(g_1) \circ \phi(g_2) = \phi(g_1 \circ g_2)$ .

Under the homomorphic mapping  $\phi$ , the subset of valid results G' forms a subgroup of H that is isomorphic to G. If we assume that failures in the computation keep us in H (i.e., failures do not cause the computation to hang or behave in some unpredictable way, but simply result in an incorrect group element), then any result that falls outside of G' is invalid and is detected as erroneous (which is the case for result  $\rho_f$  in Figure 2-1). In particular, if we model<sup>2</sup>  $\rho_f$  as  $\phi(g_1) \diamond \phi(g_2) \diamond e \equiv \rho \diamond e$  (where e is an element in the error set  $E = \{1_{\diamond}, e_1, e_2, ...\}$ ), then error detection and correction are based on the structure of the cosets of G' in H (i.e., on the factor or quotient group H/G', [49]). In the absence of failures results lie in the zero coset (that is, in G' itself). Every detectable error  $e_d \in E$  forces the result of the computation into a non-zero coset (i.e.,  $G' \diamond e_d \neq G'$ ), while every correctable error  $e_c \in E$  forces the result into a coset that is uniquely associated with that particular error (i.e.,  $G' \diamond e_c \neq G' \diamond e_j$  for every  $e_c, e_j$  in E such that  $e_j \neq e_c$ ). In Figure 2-1, if e is a correctable error, then  $\hat{\rho} = \rho$  and  $\hat{r} = r$ .

One of the most important results in [8] (also presented in [9]) is obtained for the special case of *separate* codes. These are codes in which redundancy is added through a separate "parity" computational system. In this case, the redundant group H is the cartesian product  $G \times T$ , where T is the group of parity symbols. Finding a suitable encoding homomorphism

<sup>&</sup>lt;sup>2</sup>Since H is a group, we can always model the result of a computation as  $\rho_f = \rho \diamond e$  where  $e = \rho^{-1} \diamond \rho_f$ . Therefore, given all possible hardware failures, we can generate the set of errors E. The identity  $1_{\phi}$  is included in E so that we can handle the fault-free case.

Figure 2-1: Fault tolerance in a group computation using a homomorphic mapping.

reduces to finding a homomorphism  $\pi$  such that  $[g,\pi(g)]$  is the element of  $H=G\times T$  corresponding to the operand g. If we impose the requirement that  $\pi$  be surjective (onto), the problem of finding all possible parity codings reduces to that of finding all surjective homomorphisms (epimorphisms) from G onto T (unlike  $\phi$ , mapping  $\pi$  maps G onto a smaller group T). This is a reasonable requirement because if  $\pi$  was not onto, then T would contain elements that are never used by the parity computation (and can therefore be eliminated). By an important homomorphism theorem from group theory [49], these epimorphisms are isomorphic to the canonical epimorphisms, namely those that map G to its quotient groups G/N, where N denotes a (normal<sup>3</sup>) subgroup of G. Hence the problem of finding all possible parity codings reduces to that of finding all possible subgroups of G.

By simply exploiting the abelian group structure, the above results were extended in [8, 9] to higher algebraic systems with an embedded group structure, such as rings, fields and vector spaces. The framework thereby embraces a large variety of arithmetic codes and Algorithm-Based Fault Tolerance schemes already developed in some other way. In the following example we discuss how  $\alpha M$  and parity check codes can be analyzed within the abelian group framework; additional examples can be found in [8].

<sup>&</sup>lt;sup>3</sup>A subgroup N of a group  $(G, \circ)$  is called *normal* if for all  $g \in G$ , the set of elements  $g \circ N \circ g^{-1}$  is contained in N. In the abelian group case considered in [8], any subgroup is trivially normal  $(g \circ N \circ g^{-1} = g \circ g^{-1} \circ N = N)$ .

Example 2.1  $\alpha M$ -codes provide fault tolerance to modulo-M addition (which takes place in  $Z_M$ , the cyclic group of order M) by multiplying each of the operands by an integer  $\alpha$  and performing modulo- $\alpha M$  addition, [87]. Such codes can be placed into the abelian group framework by using the injective homomorphism  $\phi:G=Z_M\longmapsto H=Z_{\alpha M}$  such that for  $g\in Z_M$ ,  $\phi(g)=\alpha g$ . Naturally, the specifics of the errors that can be detected or corrected depend very much on the actual hardware implementation and on the particular values of M and  $\alpha$ . For instance, with M=5 and  $\alpha=11$ , this arithmetic code can detect all failures that result in single-bit errors in a digitally implemented binary adder, [87]. In these implementations the operands and the result have a binary representation (i.e., 0 maps to 00000, 1 maps to 00001, etc.) and failures flip a "0" to a "1" and vice-versa.

An alternative way of providing fault tolerance to modulo-M addition is by performing a parity check using a separate (parity) adder alongside the original one. Using the algebraic framework we are able to enumerate and identify all appropriate parity computations (additions) that can be performed. More specifically, we know that each parity computation needs to lie in a group T that is isomorphic to a quotient group  $Z_M/N$  for a normal subgroup N of  $Z_M$ . Using standard results on cyclic groups [55], we conclude that all such groups T are isomorphic to  $Z_P$  where P is a divisor of M. Therefore, all parity computations for modulo-M addition are given by modulo-P addition (where P is a divisor of M).

#### 2.2.2 Fault Tolerance in Semigroup Computations

The results for the abelian group case were extended to computations occurring in a semigroup in [43, 44]. A semigroup  $(S, \circ)$  is a set of elements S that is closed under an associative

binary operation (denoted by  $\circ$ ). Clearly, every group is a semigroup; familiar examples of

semigroups that are not groups are the set of integers under the operation of multiplication,

the set of nonnegative integers under addition and the set of polynomials with real-number

coefficients under the operation of polynomial multiplication. All of the above examples are

abelian semigroups in which the underlying operation  $\circ$  is commutative (for all  $s_1, s_2 \in S$ ,  $s_1 \circ s_2 = s_2 \circ s_1$ ). Examples of non-abelian semigroups are the set of polynomials under

polynomial substitution and the set of  $M \times M$  matrices under matrix multiplication. Other

semigroups, as well as theoretical analysis, can be found in [65, 66].

A semigroup S is called a monoid when it possesses an identity element. The identity

element, denoted by  $1_{\circ}$ , is the *unique* element that satisfies  $s \circ 1_{\circ} = 1_{\circ} \circ s = s$  for all  $s \in S$ . We can focus on monoids without loss of generality because an identity element can always be adjoined to a semigroup that does not initially posses one. (The construction is straightforward: let  $S^1 = S \cup \{1_{\circ}\}$  and define  $s \circ 1_{\circ} = 1_{\circ} \circ s = s$  for all  $s \in S^1$ ; all other products in  $S^1$  are defined just as in S. By definition, element  $1_{\circ}$  is the identity of  $S^1$ .)

In order to protect a computation in a monoid  $(S, \circ)$ , we follow the model of Figure 1-1. To introduce the redundancy needed for fault tolerance, we map the computation  $s_1 \circ s_2$  in  $(S, \circ)$  to a computation  $\phi_1(s_1) \diamond \phi_2(s_2)$  in a larger monoid  $(H, \diamond)$ . The encoding mappings  $\phi_1$  and  $\phi_2$  are used to encode the first and second operands respectively (the results can be generalized to more than two operands). After performing the redundant computation  $\phi_1(s_1) \diamond \phi_2(s_2)$  in H, we obtain a (possibly faulty) result  $\rho_f$ , which we assume still lies in H. Again, we perform error-correction through a mapping  $\alpha$  and decoding through a one-to-one mapping  $\sigma: S' \longmapsto S$  (where  $S' = \{\phi_1(s_1) \diamond \phi_2(s_2) \mid s_1, s_2 \in S\}$  is the subset of valid results in H).

Under fault-free conditions, the decoding mapping  $\sigma$  satisfies:

$$\sigma(\phi_1(s_1) \diamond \phi_2(s_2)) = s_1 \circ s_2$$

for all  $s_1, s_2 \in S$ . Since we have assumed that  $\sigma$  is one-to-one, the inverse mapping  $\sigma^{-1}$ :  $S \longmapsto S'$  is well-defined and satisfies  $\sigma^{-1}(s_1 \circ s_2) = \phi_1(s_1) \circ \phi_2(s_2)$ . If we assume further that both  $\phi_1$  and  $\phi_2$  map the identity of S to the identity of H, then by setting  $s_2 = 1_\circ$ , we get  $\sigma^{-1}(s_1) = \phi_1(s_1)$  for all  $s_1 \in S$  (because  $\phi_2(1_\circ) = 1_\circ$ ). Similarly,  $\sigma^{-1}(s_2) = \phi_2(s_2)$  for all  $s_2 \in S$ , and we conclude that  $\sigma^{-1} = \phi_1 = \phi_2 \equiv \phi$ . Note that (i)  $\phi(s_1 \circ s_2) = \phi(s_1) \circ \phi(s_2)$ , and (ii)  $\phi(1_\circ) = 1_\circ$ . Condition (i) is the defining property of a semigroup homomorphism, [66, 65]. A monoid homomorphism is additionally required to satisfy condition (ii), [55, 42]. Mapping  $\phi$  is thus an injective monoid homomorphism, which maps the original computation in S into a larger monoid that contains an isomorphic copy of S.

The generalization of the framework of [8] to monoids allows non-abelian computations, for which inverses might not exist, to be treated algebraically. The generalization to monoids, however, comes at a cost since error detection and correction can no longer be based on coset constructions. The problem is two-fold: first, in a semigroup setting we may be unable to model the possibly faulty result  $\rho_f$  as  $\phi(s_1) \diamond \phi(s_2) \diamond e$  for some element e in H (because inverses do not necessarily exist in H and because the semigroup may be non-abelian); second, unlike the subgroup G' of valid results, the subsemigroup S' does not necessarily induce a natural partitioning<sup>4</sup> on the semigroup H. (For instance, it is possible that the set  $S' \diamond h$  is a strict subset of S' for all  $h \in H$ .) Conditions for single-error detection and correction are discussed in Appendix A.

If the redundant monoid H is a cartesian product of the form  $S \times T$ , where  $(S, \circ)$  is the original monoid and  $(T, \odot)$  is the "parity" monoid, then the corresponding encoding mapping  $\phi$  can be expressed as  $\phi(s) = [s, \pi(s)]$  for all  $s \in S$  and an appropriate mapping  $\pi$ . In such case, the set of valid results is given by  $\{[s, \pi(s)] \mid s \in S\}$  and error-detection simply verifies that the result is of this particular form.